CHAMELEON - µLP SoC chassis IP platform

Open, user-configurable IP platform

supporting CPUs from any vendor

Scalable AMBA-based chassis enabling maximum

energy-efficiency for SoCs in days

Technology for better future

Moving data and decision to the cloud led the whole industry to a new power and time-consuming challenge: the data deluge.

The solution to deal with data deluge, while preventing the increase of power consumed by data centers, is known as Edge AI. This solution consists in transferring most of the processing intelligence from the cloud to the sensor.

It translates into an unprecedented need to increase performances of «smart devices» by a factor of 1,000 at constant energy consumption.

Benefits are multiples:

- Faster response time

- No need for constant connectivity

- Higher data privacy

- Longer battery lifetime

The stake is to select cost-effective solutions enabling to reduce drastically the power consumption of such local decisions.

HERE COMES CHAMELEON MCU SUB-SYSTEM

Event-Based MCU Sub-system

CHAMELEON is a flexible & pre-verified event-based MCU sub-system platform embedding several standard peripherals, an autonomous DMA, a fined-grained power management unit, a tiny ML accelerator, a low latency interconnect, and an event manager.

It allows fast and efficient CPU-less data collection & filtering, enabling extremely low power consumption in both deep sleep and active modes.

CHAMELEON is preinstanciated for Cortex M and can be configured for other cores.

It is fully interoperable with our SPIDER power management platform.

The platform comes with an RTL configurator tool and all necessary drivers.

BRING DIFFERENTIATION TO YOUR CHIP ON YOUR TARGETED MARKET

ULTIMATE ENERGY EFFICIENCY

- Autonomous ULP data collection for IoT devices

- Highly energy efficient data processing for endpoint AI devices

Download our white paper “At the heart of data processing”

In order to implement efficient data processing solutions at the edge, MCU architectures need to be modified.

Firstly, an efficient fine-grained data power network needs to be implemented, optimizing not only leakage, but also dynamic power.

Then a new sensor-centric approach must be implemented, to avoid involving the CPU in all events in the case of large data collection.

- The need for more and more edge processing capability

- Limitations of current MCU solutions

- What needs to be changed

- Dolphin Design SPEED MCU subsystem and computing platform offer

- Benchmarks

- Example of audio applications

- Take-away

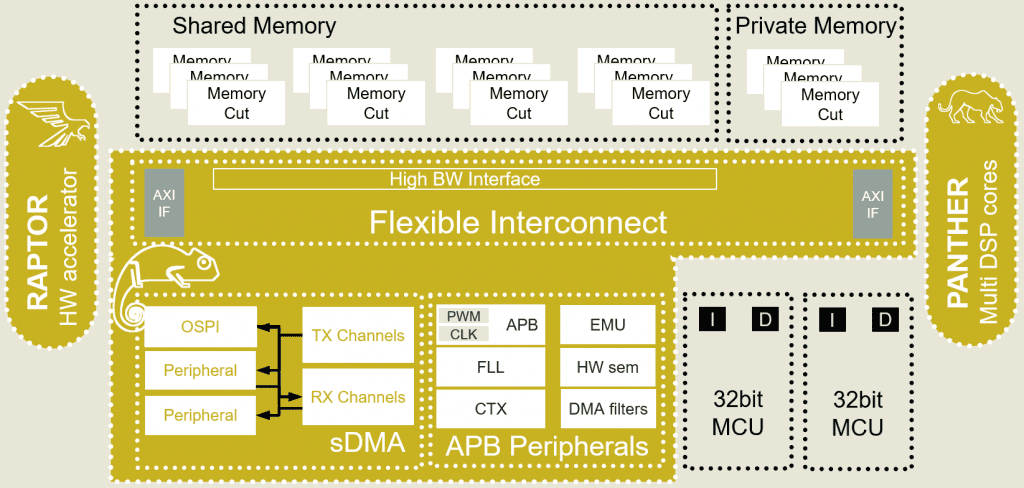

BRAIN CONFIGURATION OF CHAMELEON

SECURE YOUR SILICON

Specific configuration for your application

Chameleon is designed to fit your application requirements. Each configuration are created by our expert SoC architects to provide you with the main features to optimize the energy efficiency of your MCU sub-system to reach your performance targets.

- Preinstanciated CortexM

- Flexible interconnect

- Debug architecture

- Event & IRQ management

- Choice of peripherals, with specific optimizations: timers, watchdog, SPI, UART, I2C, GPIO

BE EFFICIENT, ADOPT CHAMELEON

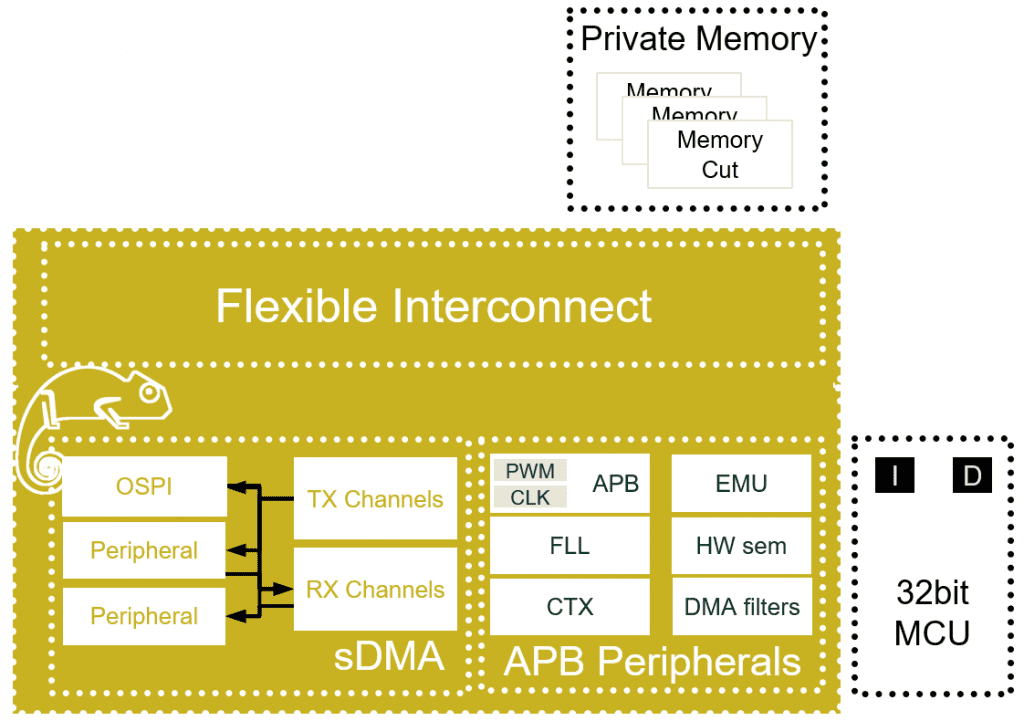

EXAMPLE: SMART CONFIGURATION

Event-based, ultra-low Power MCU fabric, dedicated to:

- Smart Sensors

- Smart TWS – Speakers

- Wearables & low-power intelligent IoT devices

PLUG & PLAY SUBSYSTEM

AI TOOL CHAIN - TensorFlowLite

DESIGN

- RTL design views

- RTL design FPGA views

- UPF description backbone

SYNTHESIS GUIDELINES

VERIFICATION

- Acceptance testbench

- Top level integration tests

DOCUMENTATION

- User manual

- Release note

TOOLS

eSW

- CMSIS Low Level HW Drivers

- Dolphin Design specific HAL drivers

- FreeRTOS

Toolsuite

- Reference to compilation toolchain

- Reference to Debug and Programming tools

Virtual Platform (On demand)

TLM design view to enable early eSW development and integration

SINGLE & DUAL CORE CORTEX M4F & M0+

Want to know more? Ask for your configuration and a detailed presentation of Chameleon, MCU Sub-system