A unique mastering of the most advanced low-power design techniques

- Near Threshold Voltage

- Adaptive Body Bias

- Power partitioning & DVFS enablement

Near Threshold Voltage

Every technology has an optimum energy point in terms of supply voltage called the minimum energy point (MEP).

MEP is usually slightly above or near the threshold voltage (NTV) of the technology. In order to leverage NTV, special libraries, compatible with low-supply voltages, are required.

We have created a unique range of NTV libraries allowing designers to enable ultra-low power consumption for the always ON domains of their SoCs.

Adaptive Body Bias

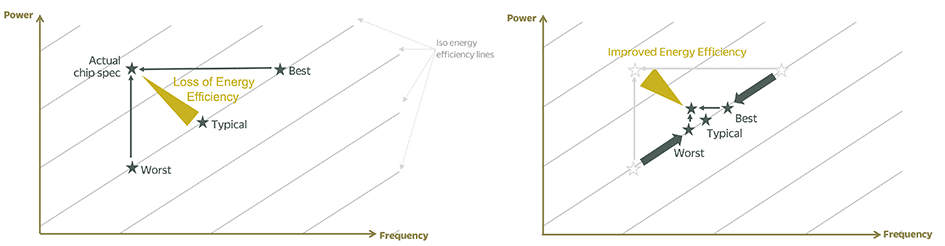

In the race for higher energy efficiency, digital designers face the impact of variations, which modify the actual chip specifications defined by the extreme variations cases (the so called “corners”). This tends to degrade significantly the energy efficiency of the chip. This is especially true at low-voltage, where temperature has a significant impact on chip performance.

To optimize the energy efficiency, SoC designers often use compensation techniques.

Through the control of transistor threshold voltage in FD-SOI technology, body bias acts as a fantastic control knob to offset all variations. Designers can design their SoCs with reduced design corners for process, temperature and aging, boosting the Power-Performance-Area (PPA) trade-off up to 10x at low voltage.

We have been cooperating with GF over the last two years to provide the market with an Adaptive Body Bias (ABB) IP solution. The ABB feature allows designers to leverage forward and reverse body bias techniques to dynamically compensate for process, supply voltage, temperature (PVT) variations and aging effects. Our ABB IP embeds the body bias voltage regulation, PVT monitors and aging sensors, and a control loop.

Power partitioning & DVFS enablement

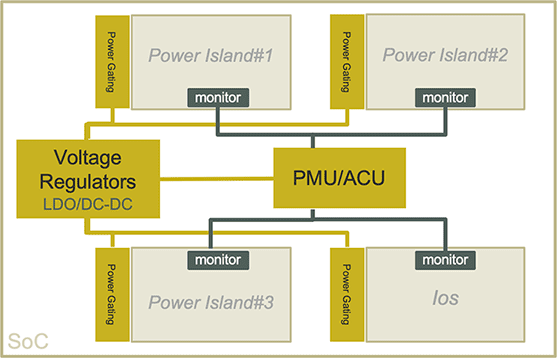

The main way to save power in modern IC design is to wake-up resources only when needed. To achieve this, designers have been using different power domains with different operating frequency points through Dynamic Voltage & Frequency Scaling (DVFS). The number of power domains and operating points has increased drastically in SoC over time, making modern low-power IC design a very complex task to manage.

IC Architects need to explore many power schemes as well as semiconductor IPs to match their SoC requirements. Once both have been selected, a lot of effort is required to validate the power architecture.

In order to ease these tasks we have developed a unique set of IPs and tools, which help architects to find and verify the optimum power scheme configuration of their SoC.

Need to discuss about your project?