With the growing chip complexity observed in many market segments, in addition to a need for longer battery life, SoC design teams are forced to adopt advanced power management techniques to improve the energy-efficiency of their devices. Recent process nodes offer a high level of SoC integration with RF connectivity, logic MCU, non-volatile memory, AI/ML processor and analog blocks on the same die, so system and power architects now have to deal with:

- Fast wake-up times to ensure instant-on operation from sleep and stand-by modes

- Control of multiple voltages on the same die to supply MCU/logic, RF, analog and SRAM domains

- Fine-grain control of power and clock gating to instantaneously switch-on / switch-off domains

- Increasing number of power modes for maximum flexibility at application-level

- Fast transitions during power mode changes to minimize energy consumption

The conventional approach for PMU design is to use a software-based solution to control the devices involved in power management. Software brings a highly flexible and configurable alternative for PMU implementation, however it requires an always-active CPU to manage the power schemes, with the penalty of hundreds of power-consuming CPU clock cycles and accesses to Flash memory.

Another approach used by design teams with more experience in power management, is to adopt hardware solutions to enable low-latency control of their power devices with decreased power consumption. However, designing full custom logic for power control requires an in-depth expertise in power management and drastically increases the design and verification cycle time. In addition, a full-custom PMU tailored for a given circuit is hardly portable and scalable to another product, even for low or mid-complexity SoC.

The ideal solution would mix the configurability of a software PMU together with the lowest power consumption of a hardware PMU.

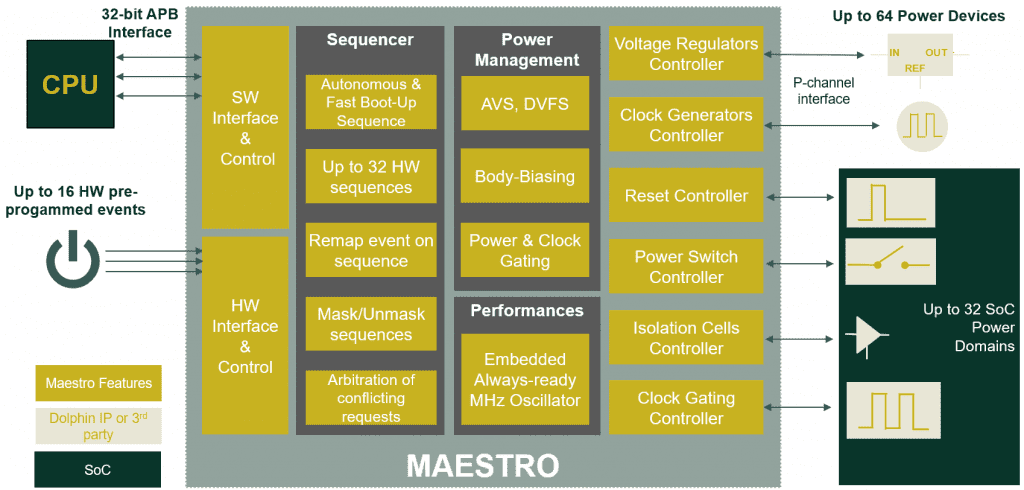

We make this possible with our latest version of MAESTRO, a unique Power Controller RTL IP which is now accompanied by PowerStudio compiler to speed-up the design of a highly scalable power controller that features breakthrough capabilities compared to traditional HW or SW PMU design methodologies.

MAESTRO features:

- Dual operation mode

o CPU-less HW operation mode for low-power and low latency control of power devices

o Flexible SW operation mode with a standard 32-bit APB interface that enables on-the-fly execution of SW-based power sequences - Embedded sequencer for autonomous control of power mode transitions, including boot-up and wake-up sequences where CPU is off

- Event-based architecture to trigger any power sequence (up to 16 pre-programmed HW events)

- Built-in always-ready 10 MHz oscillator to enable fast wake-up when RTC clocks are shutdown

- Fine-grain control of power devices (regulators, clock generators) with standard p-channel interface, enabling smooth support of both IP from Dolphin Design or 3rd party provider

MAESTRO is now augmented with PowerStudio compiler to enable a faster path from architecture to integration, featuring:

- Power State Table and Power Mode Changes GUI for fast configuration: design in a single day, iterate in a single hour

- MAESTRO gate count & transition time calculator

- Automated generation of MAESTRO RTL configuration

- Automated generation of UPF test-bench for PMU in-context verification

MAESTRO is currently being used to enable multiple customer tape-outs in various silicon technology nodes, including FD-SOI and bulk technologies.

Design an energy efficient power management system in days, not months. Do more, with less energy.

Adopt MAESTRO.