Grenoble,

France – June 12th, 2020

The MCU market is facing a profound revolution to address the challenges of data processing for edge computing IoT applications. Traditional MCU subsystem architectures have too many limitations to keep pace with the edge and very edge computing market requirements for energy efficiency. New solutions have to be implemented.

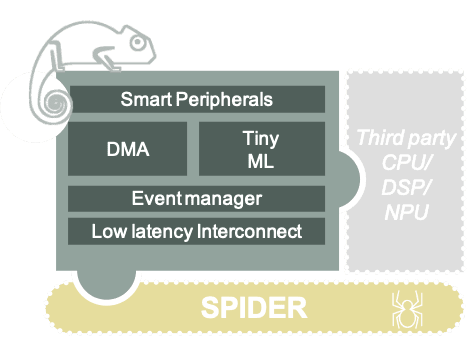

We have unlocked these limitations by implementing a disruptive architecture based on a CPU-less and event-based data management system. This new subsystem architecture, called CHAMELEON, is compatible with any CPU, DSP and NPU through a standard AMBA interface.

CHAMELEON flexibility allows front-end designers to accelerate their design cycle, using a full plug and play approach along with all necessary drivers and RTL configuration tools.

CHAMELEON comes pre-verified and silicon proven on various process nodes. It is fully interoperable with our SPIDER power management platform to achieve the highest possible level of energy efficiency.

Choose the innovative architecture. Do more, with less energy.

Adopt CHAMELEON.